Allegro MicroSystems電流傳感器IC可以分為三大類:需要外部磁芯的傳感器、具有封裝內置磁芯的傳感器,以及具有集成載流環(但無磁芯)的傳感器。最后一類就是具有共模場抑制(CMR)功能的傳感器。本文將探討CMR的機制,并重點介紹如何充分利用此機制來優化電路板設計和布局。

背景

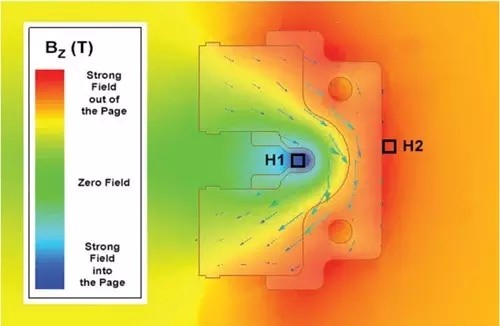

在使用集成載流環的IC中,載流環可以產生IC能測量的磁場。該磁場通過霍爾效應轉換成電壓。此霍爾電壓正比于電流大小和方向。圖1是特定電流傳感器IC引線框產生磁場的示例。在該圖中,箭頭指示通過引線框的電流,彩色圖表示100A直流電通過傳感器時產生的磁場。為了表達清晰,圖中移除了電流源。

圖1:ACS780電流傳感器引線框磁場。

使用配備集成載流環的IC具有很多優勢:無需磁芯、基本沒有磁滯、功率低、并且具有較高的溫度精確度。但是,由于不存在磁芯,傳感器容易受到磁體或傳感器IC周圍導線電流產生的雜散磁場的影響。為了抑制雜散磁場的出現,Allegro的很多電流傳感器都具有雙霍爾共模抑制方案。霍爾板的布置方式要確保當電流通過IC集成導體或載流環時,每個霍爾板感應的場極性相反。在圖1中,兩個霍爾板的位置用H1和H2表示。可以從圖中看出,這兩個區域具有方向相反的磁場。

采用CMR技術的基本原理是:如果兩個霍爾板的信號相減,然后可以將集成環引發的信號求和,這樣就可以抑制來自進入IC的任何雜散磁場共模(單極)信號。簡單舉例,假定每個霍爾板的磁場±B大小相等,方向相反,則:

H1 – H2 ∝ B1 – B2

B – B2 = B – (–B)

B – (–B) = 2 × B

因此,H1 – H2 ∝ 2 × B

假定兩個霍爾板上具有相等的雜散磁場Bext,則:

H1 – H2 ∝ B1 – B2

B1 – B2 = (B + Bext ) – (–B + Bext)

(B + Bext ) – (–B + Bext ) = 2 × B + Bext – Bext

2 × B + Bext – Bext = 2 × B

因此,H1 – H2 ∝ 2 × B

Allego的其它技術資料《無磁芯霍爾效應電流傳感器IC采用的共模場抑制技術》更詳細地介紹了CMR技術的理論和指導方程。本文介紹的主要技術是如何設計和布置這些電流傳感器IC的載流線路。此外,本文也提供了最小化其他雜散來源的指南。

臨近電流產生的磁場

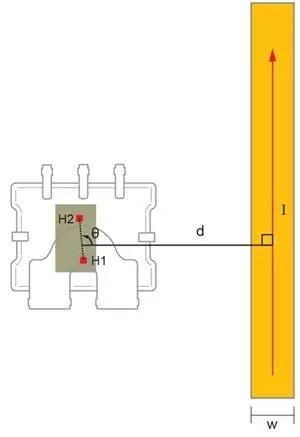

為了充分利用這些器件的CMR功能,包含IC的電路板應設計為兩個霍爾板的外部磁場相同。這有助于最大限度減少載流PCB自身產生的外部磁場導致的錯誤。每個載流軌跡的三個主要參數據決定了導致IC錯誤:與IC的距離、載流體的寬度以及它和IC之間的角度。圖2是IC附近載流體布線的示例。器件和導體之間的距離d是器件中心與導體中心的距離,電流路徑寬度為w,器件和電流路徑之間的角度θ是指連接兩個霍爾板的直線與電流路徑垂直線的夾角。

圖2:具有臨近電流路徑的ACS780(從傳感器底部觀察)。

兩個霍爾板的位置和方向隨IC的不同而有所變化。例如,如圖3所示,ACS724的霍爾板相比ACS780霍爾板旋轉了90°。如果在任何具有CMR功能的Allegro、電流傳感器IC附近進行電流路徑布線,最好保持θ盡可能接近90°。

圖3:霍爾板對齊的ACS724電流傳感器IC。

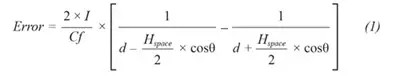

如果無法保持θ接近90°,下一個最好的選擇是保持電流路徑與電流傳感器IC之間距離d盡可能大。假定電流路徑與IC的夾角最差,即θ=0°或180°,見下列等式:

此處,H距離是兩個霍爾板之間的距離,Cf是IC耦合因數。此耦合因數隨IC不同而變化。ACS780的耦合因數是5至5.5G/A,而其他Allegro IC的耦合因數范圍是10至15G/A。

誤差估計

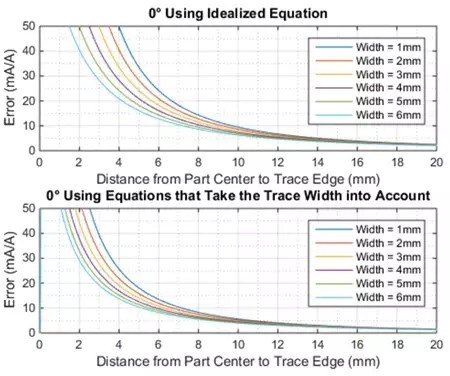

等式1假定是無限長、無限細的導線。它沒有考慮載流導體的寬度和厚度。圖4是在最差條件方向(θ = 0° 或180°)計算得出的通過ACS780的載流體誤差。該誤差是采用理想等式以及考慮導體寬度和厚度的計算密集方程組計算得出。該圖顯示,計算誤差高于使用理想方程的結果。因此,方程1可用于快速、保守估計誤差。

圖4:ACS780使用理想方程1與使用軌跡尺寸計算誤差。

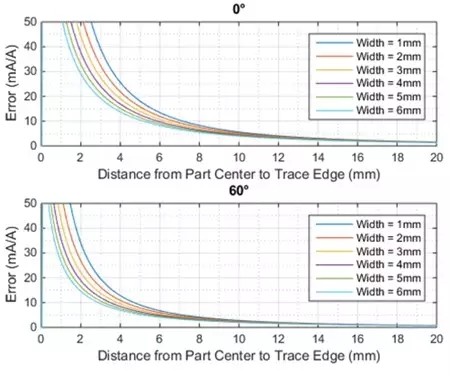

使用更精確的計算方法可以為不同寬度的電流路徑以及器件和電流路徑之間不同的角度計算誤差。對于所有角度和寬度,都假定使用4盎司規格銅導體設定電流軌跡厚度。該圖表明,載流體寬度對誤差有影響,但最大的影響因素是與器件的角度θ以及與器件的距離d。

圖5:ACS780計算4盎司規格銅導體軌跡導致的誤差;多軌跡寬度θ=0°和60°

其他需要考慮的布局原則

如果布置包含具有CMR的Allegro電流傳感器IC的電路板,所有載流路徑的方向和接近性是重要因素,但優化IC性能還要考慮其他因素。可能影響系統誤差的其他雜散場來源包括與IC集成載流體相連的軌跡以及臨近永久磁體的位置。

必須小心規劃電路板與電流傳感器IC的連接方式。可能影響性能的常見錯誤是:

·電流路徑到IP管腳的接近角度

·電流軌跡在IC下面擴展得過遠